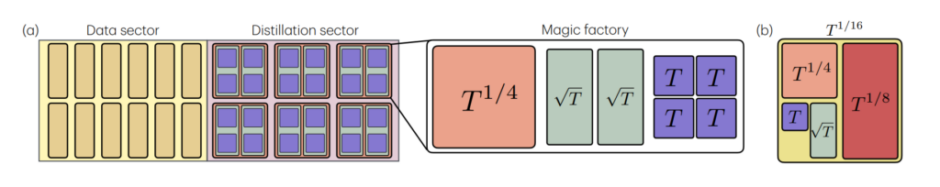

ParityQCとインスブルック大学の物理学者が、非クリフォードゲートに必要なリソースオーバーヘッドを削減するために設計された耐故障量子コンピューティング(FTQC)スキームである「Parity-Unfolded Distillation Architecture」を発表しました。この研究は、プレプリント「Parity-unfolded distillation architecture for noise-biased platforms」で詳細に説明されており、クリフォード階層の任意のレベルから回転ゲートを蒸留するためのフレームワークを提供します。このアプローチにより、従来の離散ゲートの長いシーケンスで近似するのではなく、小角回転を直接準備およびテレポーテーションすることが可能になり、通常はエラーのリスクが増加します。

このアーキテクチャは、デコヒーレンスエラーが他のタイプのノイズよりもはるかに頻繁に発生するような、ノイズバイアスプラットフォームに特に最適化されています。標準的なプロトコルでは、デリケートな量子操作を保護するために複雑で高次元の量子ビット接続が必要になることが多いですが、チームの「パリティ展開」手順により、これらのゲートは最近傍相互作用を持つ標準的な2次元平面チップで実装できます。ゲート蒸留プロセスをハードウェアの物理的制約に適応させることで、このアーキテクチャは、耐故障保護を維持しながら、従来の接続ボトルネックを回避します。

ここから先は

432字