最近の研究で、量子低密度パリティチェック(QLDPC)符号を利用した耐故障性量子コンピューティング(FTQC)のための2つの異なるアーキテクチャ設計図が発表されました。IonQのチームはイオントラップシステム向けに「ウォーキングキャット」アーキテクチャを提案し、デューク大学、テキサス大学オースティン校、イェール大学の研究者たちは中性原子アレイ向けの並列化スキームを詳細に説明しました。両論文とも、量子誤り訂正(QEC)の「時空間」オーバーヘッドに対処し、大規模シミュレーションに必要な物理量子ビット数を削減するために、量子ビットの輸送や再構成可能な接続性といったハードウェア固有の強みに焦点を当てています。

ウォーキングキャットアーキテクチャは、量子電荷結合デバイス(QCCD)チップ内でのイオンの移動性を活用して、非局所的なQLDPC符号を実装します。この設計では、「キャットファクトリー」を使用して、論理演算のバックボーンとなる複数の量子ビットのエンタングル状態を生成します。主要な技術的成果は、[[102, 22, 9]]符号を使用した高密度メモリインスタンスであり、これは22個の論理量子ビットを102個の物理量子ビットにエンコードします。IonQは、100サイトのハイゼンベルクモデルシミュレーションにおいて、10,000個の物理量子ビットと約1ヶ月の実行時間を必要とすると見積もっています。

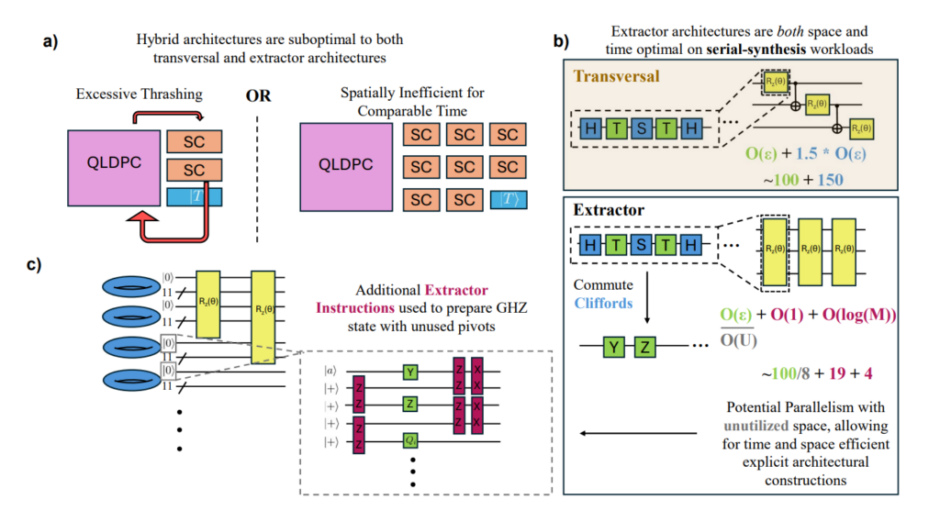

中性原子の設計図は、原子アレイプラットフォームに固有の「測定ボトルネック」に焦点を当てています。このプラットフォームでは、測定時間がゲート操作よりも大幅に遅くなります。これを軽減するために、研究者たちは、QLDPCモジュール内の未使用スペースを利用して非クリフォードゲートの注入を並列化する、テレポートベースのスキームを導入しました。このアプローチは、物理量子ビットのフットプリントを増やさずに、シリアルな「エクストラクター」アーキテクチャと比較してシミュレーションで3倍の高速化を達成しました。このチームは、約15時間でハミルトニアンダイナミクスシミュレーションを実行できる11,495個の原子を使用する構成を特定しました。

ここから先は

605字