Riverlaneは、ローカルクラスタリングデコーダー(LCD)の論文がNature Communicationsに掲載され、リアルタイム量子誤り訂正(QEC)のためのハードウェア統合ソリューションを実証したと発表しました。LCDは、リアルタイム速度(1ラウンドあたり1マイクロ秒未満)、高精度、適応性能を同時に実現する初のハードウェアデコーダーチップです。この同時達成は、エラーデータ(シンドローム)が古典的なコントローラーの処理速度よりも速く蓄積してしまう「バックログ問題」にとって極めて重要です。

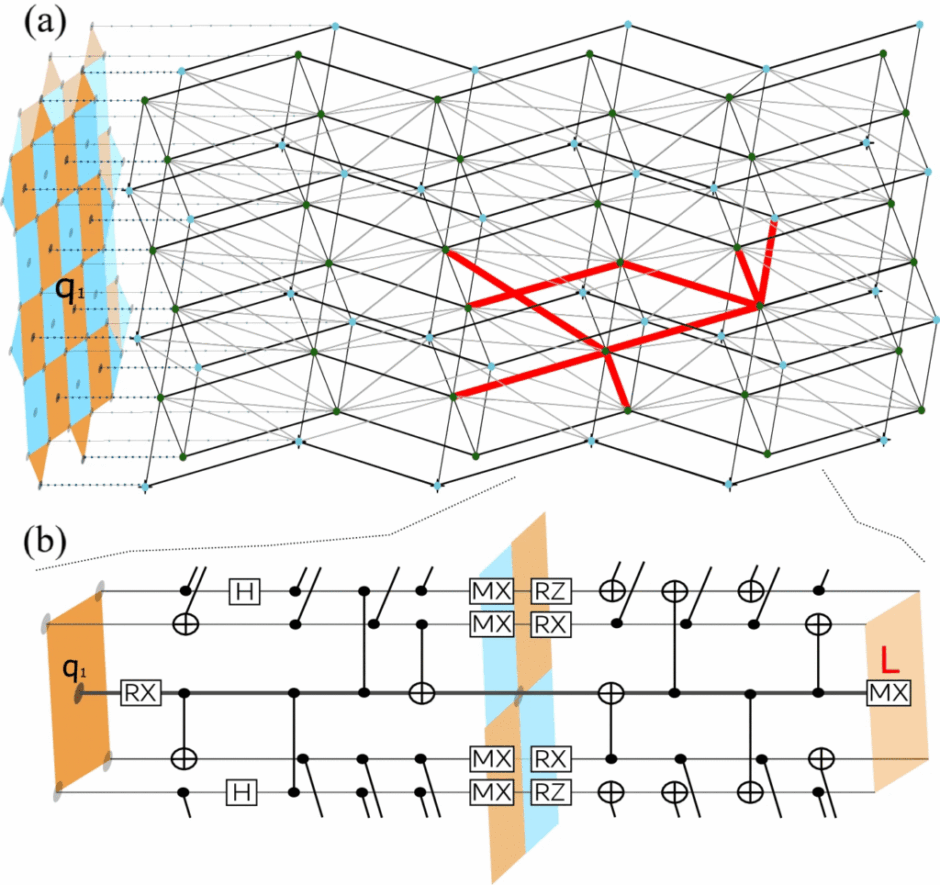

FPGAハードウェアに実装されたLCDアーキテクチャは、スループットとリソース効率のバランスをとるために、粗粒度の並列設計を採用しています。これは、近くの量子ビットエラーをクラスターにグループ化し、並列に解決することで機能します。この方法は、多くの主要な量子ハードウェアプロバイダーが使用するサーフェスコードアーキテクチャに自然に適しています。

ここから先は

841字