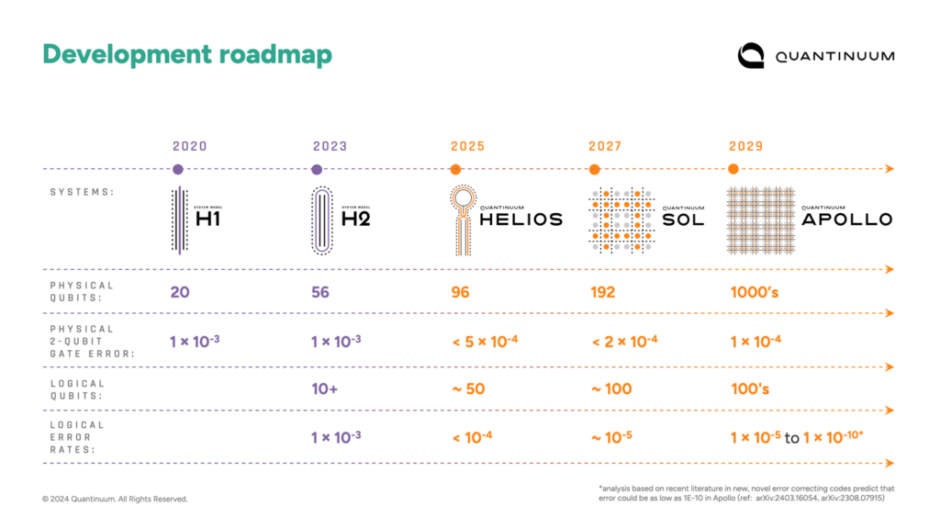

Quantum World Congressイベントで、Quantinuumは、今後数年間でユーザーに量子優位性をもたらすシステムを提供することを目標とした、量子プロセッサ開発ロードマップを発表しました。このロードマップは、H1およびH2世代のプロセッサで継続的に進歩してきた成果に基づいており、2029年までのさらに3世代にわたってロードマップが延長されています。

Quantinuumは、2019年に導入された最初のH0プロセッサから始まり、長年にわたって量子ビット数と量子ビットの忠実度を向上させ続けてきた実績があります。今後、彼らは32から56のトラップイオン量子ビットへのH2の拡張と、2量子ビットゲートの忠実度を99.9%近くに向上させた、56量子ビットH2プロセッサの最新の成果に基づいて構築しています。彼らはまた、コロラド大学ボルダー校とMicrosoftとの共同研究で示されているように、誤り訂正コードの研究を活用します。彼らは、H2プロセッサ上で12の論理量子ビットを作成するためにMicrosoftと行ったデモンストレーションを発表したばかりで、回路の論理エラー率が回路の対応する物理エラー率に対して最大22倍向上しています。

今後、2025年に導入が予定されているQuantinuumの次のシステムはHeliosと呼ばれます。量子ビット数を96量子ビットに増やし、物理エラー率を2倍の5×10-4未満にさらに改善します。誤り訂正により、このシステムは論理エラー率が約10-4の50の論理量子ビットを提供するはずです。上の図に示すように、Heliosには二股のフォークのような興味深いトポロジーがあります。

第4世代のSolデバイスの導入により、2027年に興味深いことが起こります。以前の世代では量子ビットが直線状に並べられていましたが、Solでは2Dグリッドトポロジーが導入されます。(Quantinuumがこの実現に向けて取り組んでいる技術開発の一部を説明するこちらの記事を参照してください。)Solデバイスは量子ビット数を192に倍増し、物理エラー率を2倍以上の2×10-4にさらに低下させます。その結果、論理エラー率が10-5の範囲で約100の論理量子ビットを提供するシステムが得られます。

Apolloという名前の最終システムは、2029年のタイムフレームに計画されています。このシステムは、数千の量子ビットを含むテクノロジーを拡張し、物理エラー率をさらに2倍の10-4に低下させます。これにより、論理エラー率が1×10-5から1×10-10の範囲で100個の論理量子ビットを持つシステムが作成されます。同社は、効率とパフォーマンスを大幅に向上させる可能性のあるさまざまな新しい誤り訂正コードを調査していると述べています。

Quantinuumの発表の詳細については、同社が提供するプレスリリースとロードマップに関するブログ記事こちらを参照できます。また、Microsoftとの誤り訂正作業について説明した別の記事をこちらに掲載しています。

2024年9月10日