量子コンピュータにエラー訂正を実装するには、さまざまな要素を組み合わせる必要があります。もちろん、物理エラー率が可能な限り低い、優れた物理量子ビットから始めたいと思うでしょう。サーフェスコード、カラーコード、q-LDPCなどのアーキテクチャで実装できるエラー訂正アルゴリズムを追加し、回路出力を確認してエラーを非常に迅速に特定し、修正できるように、高速なリアルタイムエラーデコーダーが必要です。エラーデコーダー部分は他の要素ほどメディアで注目されていませんが、ソリューションの非常に重要な部分です。 Riverlaneは、Deltaflowという一連のソリューションでこのための製品を提供することに注力しています。Deltaflowソリューションは、エラーを特定して修正命令を送信するための強力なエラーデコーディングレイヤー、コンピュータの制御システムと通信するユニバーサルインターフェイス、アクティビティを調整するためのオーケストレーションレイヤーで構成されています。

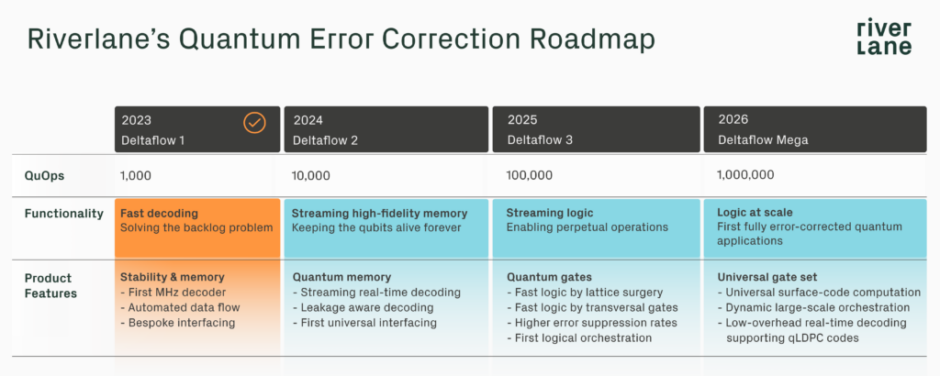

Riverlaneは、Deltaflowエラー訂正スタックロードマップをリリースしました。このロードマップは、QuOps(エラーのない量子演算)の数を毎年10倍に増やすための技術の年次アップデートを示しています。昨年、Deltaflow 1ソリューションの一部であるDD1と呼ばれるチップについて 報告しました。このチップは、サーフェスコードエラー訂正アルゴリズムを使用して1,000 QuOpsをサポートできます。そして今、Riverlaneは今年後半にDeltaflow 2で10,000 QuOps、2025年にDeltaflow 3で100,000 QuOps、2026年にDeltaflow Megaソリューションで1,000,000 QuOps(MegaQuopsとも呼ばれます)を実現するソリューションを定義しています。

Riverlaneがこれらの設計で強調している特徴の1つは、遅延を低く抑えるためにリアルタイムでデコードを実行することです。補助データを古典コンピュータに送信してエラーを特定するのは学術論文では問題ありませんが、操作が完了するまで数ミリ秒かかる場合があります。これは、実際のジョブを実行する本番環境では問題になります。Deltaflowチップを使用すると、これらの操作はメガヘルツレートで実行でき、Riverlaneはストリーミング、スライドウィンドウ、並列デコードアプローチなどの手法を実装して、デコーダーチップのスループットを可能な限り向上させています。将来のチップでは、格子手術や横断CZゲートなどのアプローチを使用して、クリフォードゲートの「高速ロジック」機能を実装する予定です。そして2026年には、ユニバーサルゲートセットをサポートするための非クリフォードゲートのサポートと、論理量子ビットを形成するために必要な物理量子ビットの数を大幅に改善できるより効率的なq-LDPCコードのサポートを提供する予定です。

彼らの技術のもう1つの重要な側面は、Riverlaneが超伝導、キャット量子ビット、スピン量子ビット、イオントラップ、中性原子、光子技術など、いくつかの異なるモダリティをサポートするようにソリューションを設計していることです。Riverlaneは、MegaQuOpsレベルのパフォーマンスを実現する量子プロセッサは、スーパーコンピュータでは実行できないシミュレーションを実行できると主張しています。

Riverlaneのエラー訂正ロードマップに関する追加情報については、 こちらのプレスリリース、 こちらと こちらのブログ記事、およびDeltaflowの こちらのWebページにアクセスできます。

2024年7月9日